## Design of Ungrounded CPW GaN-on-Si Circuit Components for High-Efficiency Power Amplifier MMICs

Philip Zurek<sup>\*(1)</sup>, Myles Foreman<sup>(1)</sup>, and Zoya Popovic<sup>(1)</sup> (1) University of Colorado, Boulder, CO, 80309

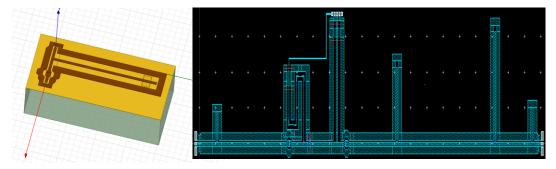

Gallium nitride (GaN) is established as a high-voltage semiconductor with broad applications, including those at microwave and millimeter-wave frequencies. At frequencies above UHF, the substrate is typically silicon carbide (SiC), which is expensive and not easily integrated with CMOS. To overcome this, GaN MMICs on silicon (Si) substrates are being developed, e.g. (R. Leblanc et al., "6W Ka Band Power Amplifier and 1.2dB NF X-Band Amplifier Using a 100nm GaN/Si Process," 2016 IEEE CSICS, Austin, TX, 2016, pp. 1-4). In this work, we explore a different GaN-on-Si process under development at the MIT Lincoln Laboratory. This process includes an epitaxially grown GaN active layer on a high-resistivity Si substrate with three metal layers and no through-via process. The goal of the work presented here is to establish a library of passive and active circuit components in coplanar waveguide (CPW) and for the specific process, with a goal of demonstrating high-efficiency GaN-on-Si power amplifier (PA) MMICs. Examples of circuit components include lines of various impedances, shorted and open stubs, tees, meander lines, and capacitors. Because the fabrication process requires the use of ungrounded CPW lines, underpasses are necessary to connect ground planes. A study of 50- $\Omega$  lines with several underpass spacings is first performed, ranging from no underpasses to underpasses spaced approximately every twentieth of a guided wavelength. All designs are simulated using HFSS and Sonnet using the GaN-on-Si process stack-up model. The fabrication process includes high-electron mobility transistors (HEMTs) of varying gate lengths (from 120 to 200 nm), periphery, gate-source spacing, and gate-drain spacing. The basic passive elements are combined with the HEMTs for several amplifier designs, starting from the available S-parameter transistor data. Since non-linear models are needed for PA design, but are not available for this new process, the output impedance is de-embedded from the measured S-parameters. The output matching networks for several PAs are designed to present a range of second and third harmonic impedances. The PA measured data can be used to make a simple nonlinear model for the devices towards improved high-efficiency PA designs.

Figure: Various CPW GaN-on-Si circuit elements: bias-tee in HFSS, PA layout.